0 引言

虚拟仪器LabVIEW目前已广泛应用于测试领域,出发点和归宿是“软件化的真实仪器”。LabVIEW同时又是一个优秀的仿真系统,但真正处于仿真目的使用的并不多见,本文提出数字“虚拟芯片”概念,并基于LabVIEW实现仿真运用。

所谓“虚拟芯片”,是在充分利用LabVIEW图形化语言风格和强大信号处理功能的基础上,设计具有一定显示界面的虚拟输入/输出端子、能完成相应的数字逻辑运算功能或数字信号处理功能的计算机程序,也就是LabVIEW的VI。应当说这是新时期数字逻辑电路设计、实验或教学的一种新举措,基于LabVIEW的数字虚拟芯片和原理图设计与其他仿真系统相比,不但有自身的特点,也是对虚拟仪器系统LabVIEW应用新领域的拓展和补充。

1 基于LabVIEW实现虚拟数字逻辑电路仿真的可行性及优点

由前面板实现数字电路的各种控制和显示,由程序流程图实现数字电路的逻辑运算功能,是基于虚拟仪器LabVIEW进行数字逻辑电路仿真设计的基础。LabVIEW的前面板提供了大量数值、布尔控件。后面板提供了大量的函数模块,使用这些函数可以很方便地调用或设计出各种门电路、编码器、译码器、运算器、存储器、触发器、定时器、ADC/DAC等数字电路设计中常用的器件模块。在数字电路中,高电平和低电平2种逻辑状态可用前面板中的布尔控件提供;而电路设计中的各种模拟量可以用各种数值型控件及函数信号发生器产生和提供。基于LabVIEW实现虚拟数字逻辑电路的可行性及优点,还表现在以下几方面:欢迎转载,本文来自电子发烧友网(http://www.elecfans.com )

(1)可充分使用LabVIEW强大的输入/输出控件资源

(2)LabVIEW中的图形化语言风格适合数字电路的逻辑图构建:

布尔控件图标与数字逻辑门电路符号相近;图形化的G语言风格适合逻辑图的连接。

(3)可开发通用或专用的数字虚拟芯片库(模块库)

(4)LabVIEW虚拟仪器可实现与外部数据的交换

2 基于LabVIEW的数字虚拟芯片设计方法

下面从一个有异步复位、置位端子的虚拟触发器单元设计开始,以LabVIEW中逻辑运算VI作为虚拟“门电路”单元,构建通用数字逻辑芯片、计数器74160虚拟“芯片”,讨论并实现该虚拟芯片的仿真应用。

2.1 具备异步复位、置位端的虚拟触发器设计

低电平有效的异步置位、复位功能的虚拟JK触发器特性方程可表示为:

当满足约束条件RD+SD=1,即RD、SD不同时为有效电平(逻辑值0)时,这2个端子可作为异步置位端(SD)和异步复位端(RD),即有:

使用过程中应当注意满足约束条件(当RD+SD=O时,始终有QN+1=O)。

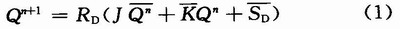

根据式(1)构建的低电平有效的异步置位、复位功能的JK触发器LabVIEW后面板如图1所示,其异步置位、复位端动作不受同步CP控制,直接实现操作(触发器状态直接被置位或复位)。为实现CP输入下降沿有效的动作方式,程序中引入了条件结构控制。当无有效CP边沿输入时,输入触发器端子的数据是J=K=“false”,等价于J=K=0,触发器处于保持状态;只有当有效CP下降沿输入时,触发器才接收输入控件J,K的数据,实现相应的动作。图1中左下角部分程序就是实现CP下降沿输入有效的控制程序部份。

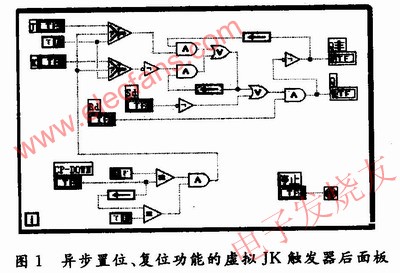

定义图1中VI的各输入、输出端子,编辑好相应的VI图标,将其保存为一独立VI文件,最后得到对应的VI图标及连线如图2所示。这样的VI图标即可看作一个虚拟触发器。

图2中2个图标为同一VI在LabVIEW中的2种不同显示方式,且2个图标为同一VI分别以不同文件名保存的2个文件。(程序完全相同)

2.2 基于虚拟JK触发器及LabVIEW虚拟“逻辑门”构

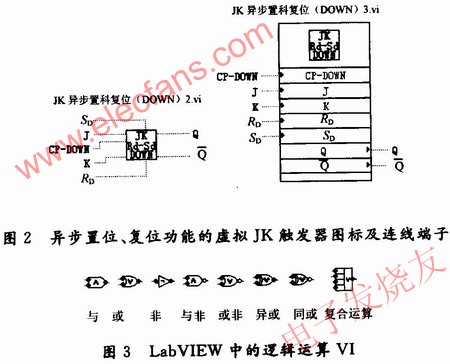

虚拟仪器LabVIEW中的逻辑运算VI,可以完成各种基本逻辑运算,在仿真数字逻辑电路时可当作虚拟的“门电路”直接使用,部份图标如图3所示。

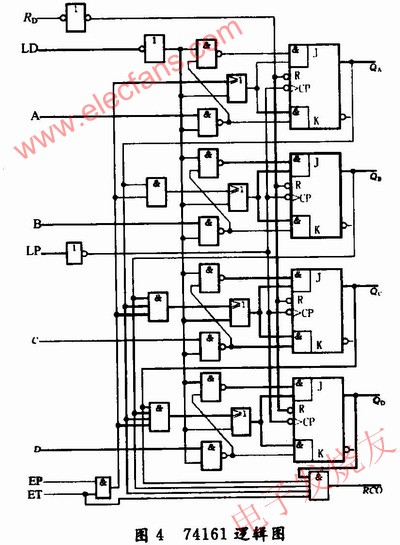

集成计数器74161的内部逻辑图如图4所示。

它是4位二进制同步加法计数器,有异步清零、预置数端子和两个使能控制端子,各端子的含义如下:

(1)RD:异步清零端,低电平有效

(2)LD:预置数使能控制端,低电平有效

(3)预置数据输入端:A、B、C、D

(4)CP;时钟输入端,上升沿有效

(5)状态输出端:QA~QD

(6)RCO:进位输出

74161的逻辑功能:

(1)异步清零功能:当RD=0时,不管其余输入端状态如何,计数器均被置零,且不受CP控制,故称为“异步清零”。

(2)同步并行预置数功能:当RD=1且LD=0时,每一个有效CP都将A、B、C、D输入端的数据传送至QA~QD状态端子接收。

(3)状态数据保持功能:当RD=LD=1,且ET·EP=0时,无论CP有无,计数器处于保持状态(QA~QD保持不变)。保持状态分2种情况:

EP=0,ET=1:进位输出RCO保持不变;ET=O,无论EP为何值,进位输出RCO=0。

(4)计数功能:当RD=LD=EP=ET=1时,电路处于正常的加法计数状态。

根据74161逻辑图,编制相应的LabVIEW后面板,结果如图5所示。从图5中可以看出,对应很好。

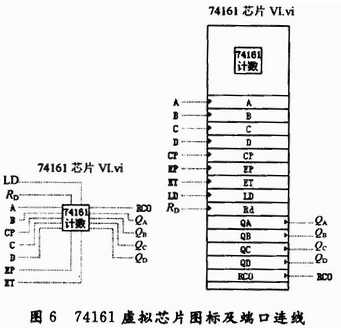

保留并定义所有输入端和输出端子,编辑图标,将程序保存为子VI,称之为虚拟74161芯片,其VI图标及连线端口如图6所示。

下面讨论虚拟芯片74161设计及应用。

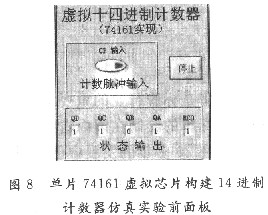

运用1片74161及LabVIEW系统中的逻辑运算VI(相当于虚拟门)图标直接连接,构建一个14进制计数器,实验后面板(虚拟逻辑图)如图7所示。

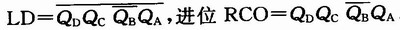

图7所示后面板中用一片74161虚拟芯片,基于74161置数归零法来实现14进制计数功能(带进位输出)。计数容量为0000~1101,置数控制端输入取

。

相应的实验前面板如图8所示。计数状态设置为RD=EP=ET=“True”,相当于逻辑1,可从CP控件手动输入计数脉冲实现计数并实验。图中显示为计数至1101时,进位输出为1的状态。当下一个CP到来时,则全部清零重新计数。

仿真实验的结果表明,虚拟74161具有实际电路芯片相同的逻辑功能。

3 时序虚拟芯片设计应注意的关键问题

对于组合逻辑,只须按逻辑图直接进行连线即可,但对于时序逻辑,应当注意下述问题:

(1)需要将状态数据缓存时,应当在数据传递过程中使用反馈节点或移位寄存器。

(2)任一触发器或时序芯片单元,在同一虚拟电路中不能重复使用(调用)文件名相同的同一子VI程序。

原因是当调用某时序子VI时,其保存的状态数据将发生变化,从而导致用到同一VI的其他经程序单元状态数据发生不可预知的错误。即虚拟电路中使用的任一时序单元对应的子Vl都应当保证是惟一的独立(子)程序,要多次使用就必须分别以不同文件名保存后再分别调用。欢迎转载,本文来自电子发烧友网(http://www.elecfans.com )

4 结语

将虚拟仪器的强大功能应用于数字逻辑电路的仿真,在虚拟仪器系统中构建各种虚拟“芯片”,并以此作为虚拟“元件”,可进一步“搭建”各种虚拟“数字电路”。虚拟仪器应用于数字电路的仿真技术,可以高效快捷地设计数字电路的原理图、分析数字电路的逻辑功能及开展基于虚拟仪器的数字电路实验、教学,同时还能拓展虚拟仪器新的应用领域。